Embedding it better...

## µTasker Document

Kinetis demo user's guide

## **Table of Contents**

| Intro | oduction                                                         | 3  |

|-------|------------------------------------------------------------------|----|

| 1.    | Preparing to start                                               | 3  |

| 2.    | Compiling the µTasker Demo using CodeWarrior v10.2               | 4  |

| 3.    | Compiling the µTasker Demo using IAR6                            | 5  |

| 4.    | Compiling the µTasker Demo using Rowely Crossworks 2.1           | 6  |

| 5.    | Compiling the µTasker Demo using Keil uVision 4.14               | 7  |

| 6.    | Compiling the Project in VisualStudio C++ and with GCC           | 8  |

| 7.    | Recommended Jumper Settings on the TWR-K60N512, TWR-K60F120M and |    |

| K70   | F120M                                                            | 9  |

| 8.    | uGLCDLIB TFT demo                                                | 10 |

| 9.    | USB CDC demo                                                     | 11 |

| 10.   | Ethernet                                                         | 12 |

| 11.   | SD Card                                                          | 14 |

| Con   | figuring the µTasker project to support firmware upload          | 15 |

| 12.   | Simulating the Kinetis K60 with the SW demo pack executable      | 16 |

| 13.   | Conclusion                                                       | 17 |

| App   | endix A – Developer's Notes                                      | 18 |

## Introduction

The  $\mu$ Tasker project has been extended to include support of the Freescale Kinetis family of devices.

This guide explains how to start using the project together with these devices based on the TWR-K60N512 board either stand-alone or together with the Tower kit, including USB, Ethernet and TFT display with touch screen.

The project includes IAR6, Rowley Crossworks 2.1, Keil uVision 4.14 and Codewarrior v10.2 (based on Eclipse) configurations as well as a stand-alone GCC make file build. In addition it allows the Kinetis and external peripherals such as the TFT display to be simulated in the  $\mu$ Tasker using VisualStudio.

Appendix A contains developer's notes concerning the Kinetis devices and also details about the operation of the  $\mu$ Tasker projects hardware related code for these parts.

## 1. Preparing to start

The minimum HW requirements for starting with the  $\mu$ Tasker project on the Kinetis K60N512 is the TWR-K60N512 module for the tower kit. This module can be powered via USB and includes an on-board OSJTAG debugger which allows loading code and debugging with either IAR6, Rowley Crossworks, uVision or Codewarrior v10.2.

When no board is available, but also generally for high-speed project development, the  $\mu$ Tasker simulator (based on Microsoft VisualStudio) can be used to simulate the processor and its peripherals for improved debugging, code development and verification efficiency.

If the complete Tower Kit is available, the TWR-K60N512 module can be used in combination with this in order to work with extended peripherals.

The first steps thus involve installing the software:

- VisualStudio C++ [µTasker simulator IDE]

- IAR6 [IDE]

- Codewarrior v10.2 [IDE]

- Rowely Crossworks for ARM V2.1 [IDE]

- Keil uVision4 for ARM V4.14 [IDE]

- P & E Kinetis Tower Toolkit [various utilities and OSJTAG drivers]

The IDEs are optional and so not all need to be installed. The P & E Kinetis Tower Toolkit should be installed (included on the CD delivered with the TWR-K60N512 board) to ensure that the debugger drivers are available.

Once the software installation has completed (a system restart may also be required) the TWR-K60N512 can be connected to the development PC via its USB device adapter (J13) and will be recognised as OSBDM debug port. Any pre-installed software on the board will now also run, allowing verification that the hardware is operational.

Since the K60N512 has 128k of SRAM it is possible to execute fairly interesting code directly from RAM rather than having to program the FLASH. As soon as the program size and its use of SRAM exceeds this amount, the project needs to be loaded to FLASH and executed from there.

## 2. Compiling the µTasker Demo using CodeWarrior v10.2

The µTasker software can be obtained on request from www.uTasker.com/Licensing/request.html.

The project is free of charge for all non-commercial use and can be evaluated for a period of 30 days for commercial purposes. Full licensing details can be read at <a href="http://www.uTasker.com/Licensing/License.html">www.uTasker.com/Licensing/License.html</a>

Precompiled target code is freely available of the software resource page: <u>www.uTasker.com/software/software.html</u> which can loaded to the board without the need to compile it.

The first time that Codewarrior is started it requires a workspace to be defined. The workspace can be located anywhere and the project will later be imported into the workspace.

Once Codewarrior has started, the µTasker project can be imported. This is achieved by selecting the context menu (right mouse click) in the "CodeWarrior Projects" window and commanding "Import…". In the import dialog the action "General | Existing Projects into Workspace" can be selected and then the root directory set to uTaskerV1.4 project directory. The import doesn't need to copy the project to the workspace.

Once the import has been executed the project is seen as uTaskerV1.4 in the CodeWarrior Project window, with two targets "MK60N512VM100\_INTERNAL\_FLASH" and "MK60N512VM100\_INTERNAL\_RAM".

Ensure that the target board is configured for the TWR-K60N512 board in the  $\mu$ Tasker V1.4 project file config.h as follows:

#define TWR\_K60N512 must be active to select the Tower board.

The project is compiled by clicking on the build button (Ctr + B will start a complete build).

The target code size is about 89k when Ethernet [including FTP, Web server, Telnet and uFileSystem], USB and TFT are active.

Smaller projects can be loaded and executed from SRAM but larger projects will need to be loaded to FLASH (MK60N512VM100\_INTERNAL\_FLASH configuration), which can be performed by executing the debug command (configure as default to load to FLASH using the OSJTAG interface).

CodeWarrior also supports loading ELF or SREC files with its Flash Programmer utility.

The project is configured to place output data (elf, s19, map file etc.) in the project directories \uTaskerV1.4\Applications\uTaskerV1.4\KinetisCodeWarrior\MK60N512VMD 100\_INTERNAL\_FLASH or

\uTaskerV1.4\Applications\uTaskerV1.4\KinetisCodeWarrior\MK60N512VMD

100\_INTERNAL\_RAM.

## 3. Compiling the µTasker Demo using IAR6

The  $\mu$ Tasker software can be obtained on request from <u>www.uTasker.com/Licensing/request.html</u>.

The project is free of charge for all non-commercial use and can be evaluated for a period of 30 days for commercial purposes. Full licensing details can be read at <a href="http://www.uTasker.com/Licensing/License.html">www.uTasker.com/Licensing/License.html</a>

Precompiled target code is freely available on the software resource page: <u>www.uTasker.com/software/software.html</u> which can loaded to the board without the need to compile it.

Open the project \Applications\uTaskerV1.4\IAR\_Kinetis\uTaskerV1.4.ewp in IAR Embedded Workbench. Select the target Debug to run from SRAM or Release to run from FLASH and ensure that the target board is configured for the TWR-K60N512 board in the  $\mu$ Tasker V1.4 project file config.h as follows:

#define TWR\_K60N512 must be active to select the Tower board.

Compile the project by pressing F7 (Project | make) or by clicking on the "Make" icon. The project should build with no errors but there may be some warnings which can be ignored. The target code size is about 78k when Ethernet [including FTP, Web server, Telnet and uFileSystem], USB and TFT are active.

In case the kick-start version is used (limited to 32k) either Ethernet can be deactivated by disabling ETH\_INTERFACE in config.h or the TFT display can be deactivated by disabling SUPPORT\_GLCD in config.h.

The debugger "PE Micro" should be selected and the code can be loaded to the board via the OSJTAG connection by clicking on the "Download and Debug" icon (with green arrow). Depending on the target selected this will be loaded either to SRAM or programmed to FLASH.

## 4. Compiling the µTasker Demo using Rowely Crossworks 2.1

The µTasker software can be obtained on request from www.uTasker.com/Licensing/request.html.

The project is free of charge for all non-commercial use and can be evaluated for a period of 30 days for commercial purposes. Full licensing details can be read at <a href="http://www.uTasker.com/Licensing/License.html">www.uTasker.com/Licensing/License.html</a>

Precompiled target code is freely available of the software resource page: <u>www.uTasker.com/software/software.html</u> which can loaded to the board without the need to compile it.

#### Open the project

#define TWR\_K60N512 must be active to select the Tower board.

Compile the project by pressing F7 (Build | Build uTaskerV14) or by clicking on the "Build" icon. The project should build with neither errors but there may be some warnings which can be ignored. The target code size is about 82k when Ethernet [including FTP, Web server, Telnet and uFileSystem], USB and TFT are active.

The debugger "Kinetis OSJTAG" should be selected and the code can be loaded to the board via the OSJTAG connection by clicking on the "Start Execution" icon (with blue arrow) - (F5)

## 5. Compiling the µTasker Demo using Keil uVision 4.14

The µTasker software can be obtained on request from <u>www.uTasker.com/Licensing/request.html</u>.

The project is free of charge for all non-commercial use and can be evaluated for a period of 30 days for commercial purposes. Full licensing details can be read at <a href="http://www.uTasker.com/Licensing/License.html">www.uTasker.com/Licensing/License.html</a>

Precompiled target code is freely available of the software resource page: <u>www.uTasker.com/software/software.html</u> which can loaded to the board without the need to compile it.

#### Open the project

$\label{eq:linear} $$ Or $$ 0.4 \ U is ion_Kinetis \ U askerV1.4 \ U askerV1.$

Ensure that the target board is configured for the TWR-K60N512 board in the  $\mu$ Tasker V1.4 project file config.h as follows:

#define TWR\_K60N512 must be active to select the Tower board.

Compile the project by pressing F7 (Project | Build target) or by clicking on the "Build" icon. The project should build with no errors but there may be some warnings which can be ignored. The target code size is about 52k when Ethernet [including FTP, Web server, Telnet and uFileSystem], USB and TFT are active.

In case the evaluation version is used (limited to 32k) either Ethernet can be deactivated by disabling ETH\_INTERFACE in config.h or the TFT display can be deactivated by disabling SUPPORT\_GLCD in config.h.

The present version of uVision4 doesn't support the OSJTAG interface and so requires a JTAG debugger to be connected (warning – the TWR-K60N512 has a fine-pitch 20 pin CORTEX connector which may require an additional adapter to connect to standard debug cables).

## 6. Compiling the Project in VisualStudio C++ and with GCC

The µTasker simulator operates with VisualStudio C++ from version 6.0 and upwards, including the free VisualStudio Express editions. This operation is detailed in the document <u>http://www.utasker.com/docs/KINETIS/uTaskerV1.4-Tutorial-Kinetis.PDF</u>

The VisualStudio environment includes also a very powerful editor and the capabilities to add post-build steps which are suitable for cross-compiling to the target hardware. As detailed in the tutorial in the link above, a target is included which will automatically perform this stage to generate a standalone binary image using the GNU compiler, plus images suitable for downloading to the target with boot loader support.

As long as the GNU compiler is installed on the PC, the project can be comfortably built from the VisualStudio environment with GCC. In this case the target configuration "Win32 uTasker kinetis plus GNU build" should be selected.

# 7. Recommended Jumper Settings on the TWR-K60N512, TWR-K60F120M and K70F120M

The TWR-K60N512 board can be used standalone but its functions are only limited since it doesn't have many peripherals that are readily accessible and it also doesn't have any onboard Ethernet physical layer device or socket. When running as standalone board the CPU is supplied with a 50MHz clock signal from a local oscillator Y1.

If the board is inserted into the tower kit and is to use the Ethernet connection on the serial board (TWR-SER) it should use a 50MHz signal supplied by the serial board via the back plane as clock. This is the 50MHz signal that is used by the PHY on the serial board, which should be synchronised to the CPU clock for proper Ethernet operation. (*See the appendix section on Ethernet for more details*).

The K60 Ethernet connection is RMII (reduced media-independent interface) and the TWR-SER board must also be correctly configured in this mode for Ethernet operation. These two configurations are shown in the following jumper table.

|                         | TWR-K60N512/<br>TWR-K53N512           | TWR-K60F120M/<br>TWR-K70F120M                                                      | TWR-SER                                                                                     |

|-------------------------|---------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Stand-alone operation   | J6 1-2 (K60)<br>J17 ON (K53)          | J18 ON (K60) or<br>J19 ON (K70)                                                    | Not applicable                                                                              |

|                         | Local 50MHz<br>oscillator input       | Local 50MHz<br>oscillator input                                                    |                                                                                             |

| Ethernet RMII operation | J6 2-3 (K60)<br>J17 OFF (K53)         | J18 OFF (K60) or<br>J19 OFF (K70)                                                  | J2 3-4 selects 50MHz clock for the PHY and the backplane                                    |

|                         | PHY Clock via<br>backplane            | PHY Clock via<br>backplane                                                         | J3 2-3 Enables 50MHz clock to<br>drive backplane line CLOCKIN0                              |

|                         |                                       |                                                                                    | J12 9-10 Sets a pull-up on the<br>PHY's CONFIG0 strap input to<br>configure it to RMII mode |

|                         |                                       |                                                                                    | J6 7-8 IRQ1 interrupt line for PHY interrupt*                                               |

| Ethernet MII operation  | eration with the TWR- possible with t | possible with the                                                                  | J2 1-2 selects 25MHz clock for the PHY (MII mode)                                           |

|                         | K60N512/TWR-<br>K53N512 but is        | TWR-K60F120M/<br>TWR-K70F120M<br>but is used with<br>the Kirin3<br>processor board | J3 2-3 – none connected                                                                     |

|                         | used with the                         |                                                                                    | J12 9-10 – none connected                                                                   |

|                         | Kirin3 processor<br>board             |                                                                                    | J6 7-8 IRQ1 interrupt line for PHY interrupt                                                |

\*The interrupt line from the PHY on the TWR-SER card can be connected to several backplane lines. **J6 7-8** should be selected on the TWR-SER board so that the IRQ1 line is selected. This is connected to port PA.27 on the K60 on the TWR-K60N512 board and PB.07 on the TWR-K53N512, TWR-K60F120M and TWR-K70F120M boards.

## 8. uGLCDLIB TFT demo

In order to see the TFT in operation the project define SUPPORT\_GLCD can be set. The TFT is selected by enabling TFT2N0369\_GLCD\_MODE.

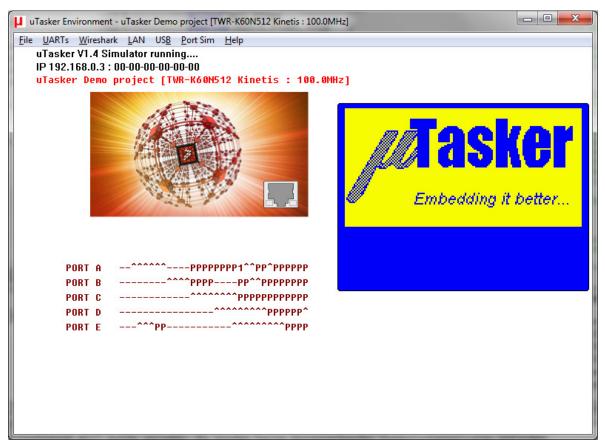

Figure 1 - TFT mono-chrome emulation mode being simulated in the  $\mu Tasker$  simulator

In order to work with the TFT display on the TWR-LCD extension board via 16-bit FlexBus it is *necessary to isolate the line FB\_AD9 from the Infra-Red input circuitry*. This can be done by removing R14 and C2 from the board or by cutting the track CMP0\_IN0 (between C2 and the back plane). With the circuitry connected the 100nF capacitor C2 otherwise heavily loads the FB\_AD9 line and so doesn't allow the bus to operate correctly at normal bus frequencies. With the modification the TFT can be controlled with a maximum FlexBus clock speed of 50MHz without any additional wait-states.

## 9. USB CDC demo

The USB CDC device demo is described in detail in the document: <u>http://www.utasker.com/docs/uTasker/uTaskerV1.3\_USB\_Demo.PDF</u>

When asked for the USB driver, use the file uTaskerFreescaleVirtualCOM.inf. This is contained in the SW demo pack or in the project directory \Applications\uTaskerV1.4\USB.

The demo document also explains loading new firmware via USB. For details about loading firmware via Web Browser and also configuring the project in CodeWarrior see the following sections of this document.

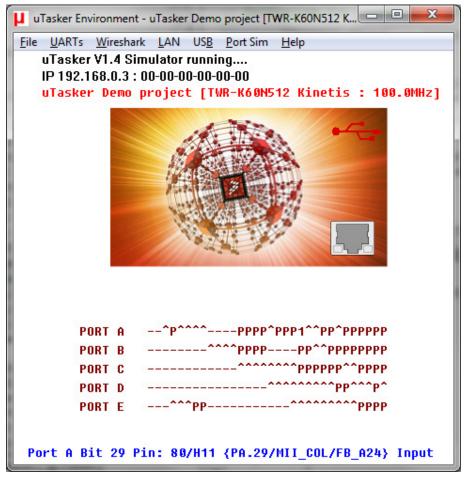

The guide explains also the  $\mu$ Tasker simulator's capability to simulate the USB part of the project, where the following shows the simulator running with enumerated USB.

Figure 2 – uTasker simulator running Kinetis, showing enumerated USB state

## 10. Ethernet

The Ethernet part of the  $\mu$ Tasker project is detailed in the Kinetis tutorial:

http://www.utasker.com/docs/KINETIS/uTaskerV1.4 Kinetis demo.PDF

The tutorial contains a description of working with the  $\mu$ Tasker simulator to fully test this functionality as well as compiling with CodeWarrior and GCC. The web pages are discussed in detail but not the method of configuring the project to work with firmware uploads. The following section contains details relevant to this task.

The web pages for the Ethernet demo are contained in the SW demo pack in the subdirectory WebPages. The default IP address if **192.168.0.3** with sub-net mask **255.255.255.0.** If this doesn't suit your test network it can be change in the command line interface via UART or USB:

- Enter the "Configure LAN Menu" by entering 1 followed by the ENTER key.

- With the command "show\_config" the present configuration can be displayed.

- Use "set\_ip\_address 192.168.1.125" to change the IP address to 192.168.1.125 (example IP address set to a value suitable for your network).

- With "save" this is committed to parameter FLASH, which will cause the board to reset and restart.

- Now test that you can ping the new address. If successful, enter into the "Configure LAN Menu" again and validate the new setting by commanding "validate". This will now commit this new address to be used permanently. Note that the new settings should be validated within a period of three minutes otherwise the temporarily saved ones will be deleted and original ones returned. See the µTasker tutorial for a full explanation of the reasons for this procedure.

- Note also that the board can be configured to obtain its IP configuration from a DHCP server "set\_dhcp enable". As long as the sub-net settings match the network it is also possible to communicate with the board using its NetBIOS name "KIRIN3" (eg. "ping KIRIN3") without needing to know its IP address. The NetBIOS name can later be changed in the web server.

- To load the web pages to the target use the bat file Copy\_all.bat, which is included in the SW demo pack or else can be found in the project directory \Applications\uTaskerV1.4\WebPages\WebPagesKinetis. If the IP address of the target has been changed, the IP address setting in the bat file will also need to be modified accordingly. The bat file will automatically transfer all web pages to the target via FTP, after which the board can be browsed using a normal web browser.

The Ethernet section of the demo contains the following main features:

- **TELNET** (command menu is accessible via TELNET and debug output is switched to it when connected)

- Web Server with demonstration of dynamic content generation, control of ports, email configuration and transmission via web command (SMPT). Display of user loaded images and firmware upload via HTTP POST.

- **FTP** server for loading web pages and firmware upload.

- NetBIOS can be contacted by name KIRIN3 (name configurable via web server)

- **DNS** (for SNMP provider resolution)

- Default IP address 192.168.0.3 (subnet mast 255.255.255.0) can be configured to other IP configuration via USB or UART menu, including DHCP.

## 11. SD Card

The demo project optionally supports a FAT file system on an SD card. This allows web complicated pages to be served from there, rather than form internal FLASH, and also allows a slide-show to be displayed on the TFT display.

There are two SD card slots available:

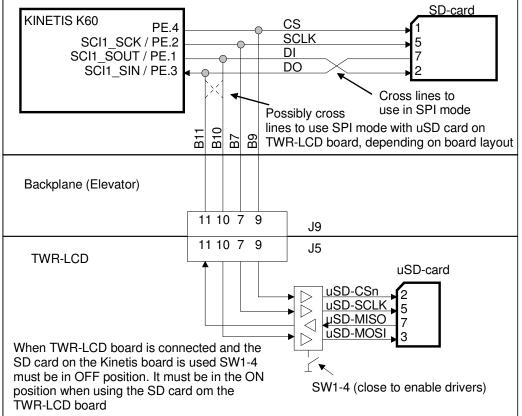

- The first is on the Kinetis K60 board and is connected to the SD controller interface of the K60, as well as to SPI1. When the demo is working in SPI mode the operation of this slot is only possible when pins 2 and 7 of the SD card connector are swapped since the SPI1 MOSI/MOSI are otherwise incorrect. **WARNING**: *Newer Tower kits may have the write protect switch of the SD card connected to the reset output (allowing the processor to reset external peripherals in the kit via the port output PTB1). In this case, when the write protect is not set in the SD card it will cause external boards to be held in reset. See the following for more details and work-around:*

http://www.utasker.com/forum/index.php?topic=1737.msg6228#msg6228

- The second is the uSD card slot on the TFT extension board. This is also connected to SPI1 on the Kinetis. To use as interface in SPI mode it is possible that the signals also need to be crossed; in this case check whether the SPI1\_SOUT signal is connected to the backplane at B10 or B11. To do this, measure it on the board since it has been found that the board doesn't necessarily correspond with the circuit diagram (Rev. C). SPI1\_OUT needs to be connected with B10 and SPI1\_SIN with B11.

In case the TWR\_LCD board is connected the switch SW1-4 much be set accordingly as shown in the following diagram:

Figure 3 – Connection to SD cards and setting for SW1-4 on the TWR-LCD board

## Configuring the µTasker project to support firmware upload

The pre-compiled target file <code>uTaskerV1.4\_KINETIS\_USB\_ETHERNET.S19</code> from the SW demo pack already contains the <code>µTasker</code> boot loader and the complete application. In this case firmware uploads can already be tested by using the following two files in the SW demo pack:

- z\_Upload\_3.bin. This is the same application but with a version number V1.4.003.. By checking the version number displayed in the web browser or via the command menus (UART, TELNET or USB) it is possible to verify that a firmware upload has been successful.

- z\_Upload\_2.bin. This is the application contained in the original target file which can be reloaded after testing z\_Upload\_3.bin or. This then displays the original version number V1.4.002.

In order to compile software to upload to the target a different target is required. The corresponding target is KINETIS\_BM\_ROM (Bare-minimum boot loader target). For full details about working with this and also the boot loader project see the boot loader documents

http://www.utasker.com/docs/uTasker/uTaskerBoot\_003.PDF

and

http://www.utasker.com/docs/uTasker/BM-Booloader for M5223X.PDF

The target to select in the CodeWarrior boot loader project is M5225X\_ROM.

To be noted are following settings for the boot loader project:

- in config.h the defines #define KIRIN3 and #define \_M5225X should be active. The first one sets the application start address to 0x1000 (after the first 4k FLASH block in the Kirin3 device) and the second configures the memory map accordingly. Note that the define KIRIN3 also automatically disables the assembler file workaround for the internal FLASH speculation address qualification incomplete errata of earlier M522XX devices.

- The demo project uses the following memory map: Boot loader occupies 2k (0..0x7ff). Application space is 128k (0x1000..0x16aff). Parameter system occupies 2 x 2k sectors (0x21000..22fff) The file system occupies 372k (0x23000..7ffff), whereby the last 128k (0x60000..0x7fffff) is intended for accepting secure firmware upload

## 12. Simulating the Kinetis K60 with the SW demo pack executable

In order to allow new users to quickly see how the  $\mu$ Tasker simulator operates, an executable is included in the corresponding SW demo pack. This can be found in the sub-directory \Simulator and started by simply double-clicking on uTaskerV1-4-KINETIS-Sim.exe.

The simulator doesn't need any installation but does require WinPCap to be installed on the PC. If you already have WireShark installed (which also uses it) no further effort is required, otherwise this can be found at <a href="http://www.wireshark.org/">http://www.wireshark.org/</a>

The simulator will be displayed as show in the screen shot earlier in this document. It has a default IP address of 192.168.0.1 and opens COM1 on the PC as UART0. This means that by connecting a cross-over cable to COM1 (or by using a virtual com port loop back to it) you can communicate with a terminal emulator (19'600 Baud) and change any settings if needed, as already described in this document and the other guides it links to. When the simulator program is terminated it will always save its complete simulated FLASH contents so that the new settings are valid the next time it is started.

You will need first to configure the PC's NIC (Network Interface Card) that it should use for mapping the Kinetis Ethernet controller to – do this in the "LAN" menu with "Select Working NIC". This setting will also be saved and thus needs only be entered once.

Then use the bat file, as described in the chapter "Ethernet", to transfer the web pages to the simulated device via FTP. After this has been done, connect to its IP address using a standard browser and see the project in operation!

The simulator allows comfortable project development and testing in the VisualStudio environment and the complete project is included as part of the  $\mu$ Tasker package.

### 13. Conclusion

This document has given a quick introduction to compiling and loading the demo software to, and running it on, the **TWR-K60N512** (in combination with the Freescale Tower Kit or standalone). As well as giving simple instructions as to how to verify that the software is correctly running is has given links to further documents containing detailed descriptions concerning the use of the USB and the Ethernet parts of the demo, as well as how the project can be configured to enable support of the firmware upload features via USB and Ethernet.

A short guide to using the simulator executable, as included in the SW demo pack, has also been given.

Modifications:

- V0.0 23.12.2011 First version - in progress

- V0.01 9.1.2011 Intermediate version - in progress

- V0.02 14.1.2011 Intermediate version - in progress

- V0.03 25.1.2011 Intermediate version – first developer's version

- V0.04 29.1.2011 Intermediate version – developer's version with new port interrupt details

- V0.05 30.1.2011 Intermediate version – developer's version with new PIT details

- V0.06 4.2.2011 Intermediate version – developer's version with new watchdog and reset details as well as UART restrictions

- V0.07 10.3.2011 Intermediate version – developer's version with new RTC, ADC, DAC, I<sup>2</sup>C details

- V0.08 23.3.2011 Intermediate version – developer's version with new SPI details

- V0.09 2.4.2011 Intermediate version – developer's version with new UART RTS/CTS

details. DMA uMemcpy(), uMemset() and mass erase command support

-V0.10 10.4.2011 Add notes about using the SD card in SPI mode and the operation of the SPI interface

-V0.11 25.04.2011 Add details about SPI control and timing of the SPI FLASH driver - V0.12 13.08.2011 Add K40 notes and SLCD

- V0.13 20.10.2011 Add RTC API details and EMAC IP accelerator details, as well as RMII PHY synchronisation

V0.14 03.02.2012: Dual FlexCAN added. FlexTimer PWM notes added.

V0.15 17.03.2012: Added K60F120M, K70F120M and K53N512 boards and details about clock module differences in the high speed parts with FPU. Extended ADC details.

V0.16 27.04.2012 Added notes about different Flash sector sizes in FPU device and DMA details

V0.17 23.6.2012 Added UART3 option on port F for K70. Added notes about RMII\_REF\_CLK on FPU parts and warning about the SD card write protect pin being connected to the peripheral reset in newer tower card versions. V0.18 27.10.2012 Added additional DAC details.

## Appendix A – Developer's Notes

These developer's notes were created during porting of the  $\mu$ Tasker project and peripheral drivers to the Kinetis. They are not intended as replacement for the Kinetis K60 user's manual but instead discuss details that may not necessarily be immediately obvious and also compare the features, operation and techniques required to those of the Coldfire project (a number of peripherals have been inherited from the Coldfire, sometimes with new enhancements).

| MK60N256VLQ100 | 64k  | 256k |

|----------------|------|------|

| MK60X256VLQ100 | 64k  | 256k |

| MK60N512VLQ100 | 128k | 512k |

| MK60N256VMD100 | 64k  | 256k |

| MK60X256VMD100 | 64k  | 256k |

| MK60N512VMD100 | 128k | 512k |

| MK60N256VLL100 | 64k  | 256k |

| MK60X256VLL100 | 64k  | 256k |

| MK60N512VLL100 | 128k | 512k |

| MK60N256VML100 | 64k  | 256k |

| MK60X256VML100 | 64k  | 256k |

| MK60N512VML100 | 128k | 512k |

The K60 devices contain the following amount of RAM and program FLASH:

The K60X versions contain in addition 256k FlexNVM and 4k FlexRAM.

Program FLASH is located from the address 0x0000000 where the reset vector is located – the first long word contains the initial stack pointer value and the second long word the initial program counter value. This is in keeping with the Cortex M4 reset mechanism, which is also the same as used by the Freescale Cortex devices.

The SRAM is centred around 0x20000000. A device with 128k SRAM will therefore have its SRAM from 0x1fff0000 to 0x20000ffff – a device with 64k SRAM 0x1fff8000..0x20007fff.

Security options are loaded from FLASH on reset. These are held in the area 0x00000400..0x0000040f which means that the correct values need to be stored in this area so that the device is not disabled for debugging, etc. When no security features are to be activated these addresses are programmed to 0x00.

By default the first 1024 bytes of FLASH are used by the reset vector and interrupt vectors. In the case of the  $\mu$ Tasker project only the reset vectors are located here and the interrupt vectors are relocated to the start of SRAM – in the case of the K60, 432 bytes of RAM are actually used, after which variables can be stored.

Between the reset vector and the security settings in FLASH there is 1016 bytes of space. Standard functions are forced into this space so that it is generally used efficiently if the compiler doesn't automatically fill it with code.

#### Clocks – devices up to 100MHz

The module is very flexible and allows various sources to be used to generate a wide range of frequencies for use by the CPU and peripherals.

When the device resets it is clocked by default an internal slow clock which has a frequency of about 32kHz (31.25kHz .. 39.0625 kHz). This is used to derive a frequency 640 times higher by using a FLL (frequency locked loop), meaning that the CPU clock frequency is in the range 20-25MHz.

[The Flash configuration parameters allow also a 1kHz slow clock default to save power when starting in very low power systems].

Due to the fact that the  $\mu$ Tasker project is used mainly for communication based projects where the clock frequencies need to be within certain tolerances (USB, UART, Ethernet) the initial clocking mode will generally not be suitable since its frequency accuracy is low. Therefore the concentration is on switching from the initial mode to a mode allowing Ethernet to operate with the CPU clocked at its maximum speed for this device of 100MHz. This is accomplished by moving through various intermediate clocking state to arrive at the final state with all circuitry locked ready for final operation.

Note that the clock source much be 50MHz for the Ethernet controller to be able to operate in RMII mode since the clock input is used as clock for this Ethernet module.

The following mode transitions (as defined by the multi-purpose clock generator module) are thus required:

FEI -> FBE -> PBE -> PEE

FEI (FLL Engaged Internal) is the initial state as described above

FBE (FLL Bypassed External) is an intermediate state where the FLL output (initially between 20MHz and 25MHz) is disconnected and the CPU is driven from the external reference clock. This enables the FLL to be configured to generate different frequencies without causing CPU clocking errors to occur. The CPU will in this case be clocked at 50MHz while the next setting is prepared.

PBE (PLL Bypassed External) is an intermediate state where the CPU is clocked from the external reference clock (50MHz in the case of the demonstration). The PLL is now enabled but its output not used, allowing it to be configured ready for the final step.

PEE (PLL Engaged External) is the final state whereby its stabilised output (set to 100MHz) is used to clock the CPU. It is locked to twice the frequency of the external clock (50MHz). The FLL is disabled in a low-power state.

The clocking configuration is set in app\_hw\_kinetis.h by specifying the external clock frequency and the PLL divide and multiplication values.

#define EXTERNAL\_CLOCK 5000000

// this must be 50MHz in order to use Ethernet in RMII mode

#define CLOCK\_DIV 16

// input must be divided to 2MHz..4MHz range (/1 to /25 possible)

#define CLOCK\_MUL 32

// the PLL multiplication factor to achieve operating frequency of

100MHz (x24 to x55 possible)

From the clock generator output the following main clock signals can be controlled by dividing by 1 to 16 times. This is also necessary in some cases to respect the maximum clocking speed of the individual buses/modules:

- System/Core clock this can be programmed with a divide value of 1 to obtain the fastest value from a 100MHz PLL output of 100MHz.

- Bus/Peripheral clock the maximum speed of the peripheral bus is 50MHz and so this requires a divide value of 2 when the PLL clock is 100MHz.

- FlexBus Clock The maximum value of the FlexBus clock is 50MHz as in the case of the bus clock.

- Flash clock The maximum Flash clock is 25MHz and so a divide by 4 is required in case of a 100MHz PLL clock output.

The FlexBus and Flash clock speeds should never be higher than the bus clock speed, even when the bus slock speed is lower than the individual maximum frequencies. The same applies to the bus clock frequency, which should never be higher than the system/code clock frequency.

The divide values are set as follows:

| #define SYSTEM_CLOCK_DIVIDE | 1 | // 1 to 16 - usually 1 |

|-----------------------------|---|------------------------|

| #define BUS_CLOCK_DIVIDE    | 2 | // 1 to 16             |

| #define FLEX_CLOCK_DIVIDE   | 2 | // 1 to 16             |

| #define FLASH_CLOCK_DIVIDE  | 4 | // 1 to 16             |

If any settings are invalid (for example an invalid divide value is attempted or a clock range is out of specification) a compiler check error is generated so that the offending value can be corrected.

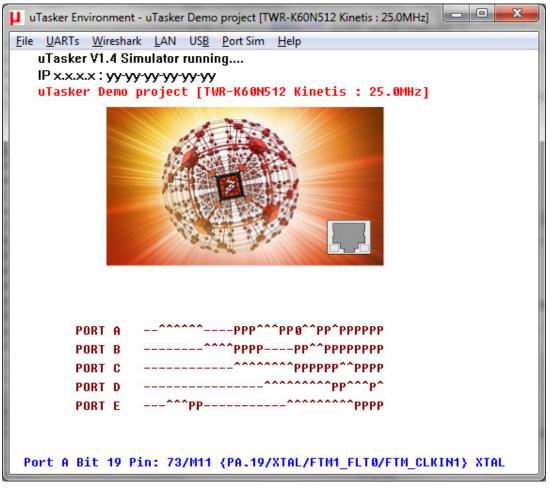

The CPU clock frequency generated by the PLL is displayed when running the simulator.

#### Clocks – devices above 100MHz

Devices with floating point unit (FPU) operate at 120MHz and above. The design of the clock module is however different.

The PLL input has a range of 8MHz to 16MHz. The pre-divider can divide the input by 1 to 8 to obtain a suitable frequency value.

The PLL multiplier has the range x16 to x47

The PLL has an additional output which is twice the PLL output speed, meaning that this output should be set to 240MHz to achieve a system clock of 120MHz. This x2 clock is optionally available for deriving peripheral frequencies from.

#### Tower TWR-K40X256 clock

This board uses an 8MHz crystal oscillator, rather than an external clock as the K60 tower board uses. This means that its clock initialisation is a bit different because it can't transition from the FEI to FBE state based on an external clock source but must enable the crystal oscillator instead.

The configuration for 96MHz is shown below:

#define CRYSTAL\_FREQUENCY 800000 // 8 MHz crystal #define \_EXTERNAL\_CLOCK CRYSTAL\_FREQUENCY #define CLOCK\_DIV 4 // input must be divided to 2MHz..4MHz range (/1 to /25 possible) #define CLOCK\_MUL 48 // the PLL multiplication factor to achieve operating frequency of 96MHz (x24 to x55 possible)

#### GPIOs

General purpose I/Os are grouped as 32 bit ports with read, write, clear, set and toggle capability. All ports are disabled (not clocked) out of reset and so they need to first be enabled before they can be used. This involves setting the bit for the particular port in the System Clock Gating Control Register 5 (SIM\_SCGC5 in the System Integration Module).

GPIOs are multiplexed with other peripheral signals and can be configured to have specific characteristics. The usual default is to be not connected (disconnected also from the GPIO functionality) or to have a default peripheral function. To be used as digital input or output they must be connected by setting each individual port bit control accordingly to GPIO function. Each GPIO input can be configured to have no pulls, pull-up or pull-down, with either a 2MHz passive input filter or a optional digital glitch filter. Each GPIO output can be configured to be push-pull or open-drain, with full-speed or limited slew rate, with full drive or limited drive strength.

By setting a lock bit the port pin configuration can be protected against further modification until the next system reset.

To cater for the need to control each individual pin the  $\mu$ Tasker port macro has been extended to automatically clock the port and include passing the characteristics of the pins when they are configured. The following shows a single GPIO being configured as an output with the initial value '1' as open-drain output with limited slew rate and high drive strength.

\_CONFIG\_DRIVE\_PORT\_OUTPUT\_VALUE(A, PORTA\_BIT11, PORTA\_BIT11, (PORT\_ODE | PORT\_SRE\_SLOW | PORT\_DSE\_HIGH));

When multiple pins are defined each of them are set to have the same configuration characteristics. The macros that include the full configuration are:

\_CONFIG\_PORT\_OUTPUT(ref, pins, chars)

\_CONFIG\_PORT\_INPUT(ref, pins, chars)

\_CONFIG\_DRIVE\_PORT\_OUTPUT\_VALUE(ref, pins, value, chars)

The  $\mu$ Tasker simulator simulates the port states out of reset so that the default function of each pin can be simply identified. Unconnected pins are displayed as inputs but are not actually connected to the GPIO input function. Pins defaulting to a peripheral function are displayed as 'P' and their exact function can be seen by hovering the mouse over the port bit.

Simulator showing the state of pins out of reset (PA.11 has been subsequenty set as output). Hovering the mouse over PA.19 shows its possible functions and that its default is XTAL

To configure a peripheral function the macro \_CONFIG\_PERIPHERAL (port, pin, function) can be used. For example:

\_CONFIG\_PERIPHERAL(A, 15, PORT\_MUX\_ALT4);

This sets the alternative function 4 to port A, bit 15. In this case it is MIIO\_TXEN on PA.15. Alternatively the following can also be used when a corresponding peripheral multiplexing define is available.

\_CONFIG\_PERIPHERAL(A, 15, PA\_15\_MII0\_TXEN);

Furthermore the characteristics of digital peripherals can also be controlled at the same time as their multiplexing is configured:

\_CONFIG\_PERIPHERAL\_VALUE(B, 17, (PORT\_MUX\_ALT5 | PORT\_DSE\_HIGH |

PORT\_PS\_DOWN\_ENABLE));

This shows the alternative 5 peripheral (FB\_AD16) being set to port B-17 with high strength and pull-down enabled

It is important to note that the ports need to be powered up to enable setting peripheral functions on them. For this reason the peripheral select macros automatically power on the ports of the peripheral pins selected.

See the following forum post for a fast port configuration macro added to the project <a href="http://www.utasker.com/forum/index.php?topic=1664.0">http://www.utasker.com/forum/index.php?topic=1664.0</a>

#### UARTS

The K60 has 6 UARTs with RXD, TXD, RTS and CTS signals.

The UARTs support infrared and ISO 7816 T0/T1 protocols.

UARTs 0 and 1 are clocked from the core/system clock, which allows highest performance potential. The other UARTs are clocked from the bus clock.

The UARTs can usually be mapped to various pins on the device. The following table shows the possibilities.

| UART0                         | UART0_TXD        | UART0_RXD        | UART0_RTS        | UART0_CTS        |  |

|-------------------------------|------------------|------------------|------------------|------------------|--|

| UARTO_A_LOW Port A2 (Alt 2) F |                  | Port A1 (Alt 2)  | Port A3 (Alt 2)  | Port A0 (Alt 2)  |  |

| default                       | Port A14 (Alt 3) | Port A15 (Alt 3) | Port A17 (Alt 3) | Port A16 (Alt 3) |  |

| UART0_ON_B                    | Port B17 (Alt 3) | Port B16 (Alt 3) | Port B2 (Alt 3)  | Port B3 (Alt 3)  |  |

| UART0_ON_D                    | *Port D7 (Alt 3) | Port D6 (Alt 3)  | Port D4 (Alt 3)  | Port D5 (Alt 3)  |  |

| UART1                         | UART1_TXD        | UART1_RXD        | UART1_RTS        | UART1_CTS        |  |

| default                       | Port E0 (Alt 3)  | Port E1 (Alt 3)  | Port E3 (Alt 3)  | Port E2 (Alt 3)  |  |

| UART1_ON_C                    | Port C4 (Alt 3)  | Port C3 (Alt 3)  | Port C1 (Alt 3)  | Port C2 (Alt 3)  |  |

| UART2                         | UART2_TXD        | UART2_RXD        | UART2_RTS        | UART2_CTS        |  |

| Default                       | Port D3 (Alt 3)  | Port D2 (Alt 3)  | Port D0 (Alt 3)  | Port D1 (Alt 3)  |  |

| <b>K70</b> –<br>UART2_ON_E    | Port E16 (Alt 3) | Port E17 (Alt 3) | Port E19 (Alt 3) | Port E18 (Alt 3) |  |

| <b>K70</b> –<br>UART2_ON_F    | Port F14 (Alt 4) | Port F13 (Alt 4) | Port F11 (Alt 4) | Port F12 (Alt 4) |  |

| UART3                         | UART3_TXD        | UART3_RXD        | UART3_RTS        | UART3_CTS        |  |

| default                       | Port E4 (Alt 3)  | Port E5 (Alt 3)  | Port E7 (Alt 3)  | Port E6 (Alt 3)  |  |

| UART3_ON_B                    | Port B11 (Alt 3) | Port B10 (Alt 3) | Port B8 (Alt 3)  | Port B9 (Alt 3)  |  |

| UART3_ON_C                    | Port C17 (Alt 3) | Port C16 (Alt 3) | Port C18 (Alt 3) | Port C19 (Alt 3) |  |

| <b>K70</b> –<br>UART3_ON_F    | Port F8 (Alt 4)  | Port F7 (Alt 4)  | Port F9 (Alt 4)  | Port F10 (Alt 4) |  |

| UART4                         | UART4_TXD        | UART4_RXD        | UART4_RTS        | UART4_CTS        |  |

| default                       | Port E24 (Alt 3) | Port E25 (Alt 3) | Port E27 (Alt 3) | Port E26 (Alt 3) |  |

| UART4_ON_C | Port C15 (Alt 3) | Port C14 (Alt 3) | Port C12 (Alt 3) | Port C13 (Alt 3) |

|------------|------------------|------------------|------------------|------------------|

| UART5      | UART5_TXD        | UART5_RXD        | UART5_RTS        | UART5_CTS        |

| default    | Port E8 (Alt 3)  | Port E9 (Alt 3)  | Port E11 (Alt 3) | Port E10 (Alt 3) |

| UART5_ON_D | Port D9 (Alt 3)  | Port D8 (Alt 3)  | Port D10 (Alt 3) | Port D11 (Alt 3) |

\*UART0\_TXD on Port D7 is special since its drive strength can be programmed by CMTUARTPAD in SIM\_SOPTS.

The  $\mu$ Tasker UART driver supports 6 channels and defaults to the pin-outs as shown in the "default" rows. By activating the alternative defines, for UARTs with multiple positions, the set of combinations can be configured accordingly.

The UARTs support 10 and 11 bit characters. That means that they can operate in 8 bit character mode with or without parity but plus one stop bit:

- start bit, 8 bit character, one stop bit)

- start bit, 8 bit character, parity bit, one stop bit)

or 7 bit character mode with parity

- start bit, 7 bit character, parity bit, one stop bit)

In addition an address bit can be used (generally known as multi-drop or 9 bit mode).

When in 7 bit character mode the parity bit is received as  $8^{th}$  bit in the receive data register and so needs to be masked out in software to avoid corruption.

This means that there are some restrictions as to what formats are possible since 1.5 or 2 stop bits cannot be configured and also 7 bit character mode without parity is not supported.

#### **RTS/CTS operation**

The UARTs support various modem modes of operation. The two most important are the control of RTS when sending on a bidirectional line (like RS485), whereby the RTS should drive the transmitter transceiver (either positive or negative), and HW flow control, whereby the RTS and CTS are used to control the flow of data between the two ends [transmitter can only send when CTS is asserted].

To control the RTS line to envelope the data transmission characters a mode is available. By enabling the bit TXRTSE in the UARTX\_MODEM the UART automatically asserts the RTS line when there is data in the output buffers and negates it automatically after the stop-bit of the last data byte has been sent. In addition the polarity of the RTS line can be controlled using the TXRTSPOL bit in the same register.

The RS485 mode can be controlled by the driver routine:

```

fnDriver(SerialHandle, (CONFIG_RTS_PIN | SET_RS485_MODE |

SET_RS485_NEG), 0);

```

When not in RS485 mode the RTS signal can be controlled by software by using

```

fnDriver(SerialHandle, (SET_RTS), 0);

```

and

fnDriver(SerialHandle, (CLEAR\_RTS), 0);

In this case the RTS line must have been configured as non-RS485. The UART negates the RTS line when CLEAR\_RTS is commanded by disabling its control based on the state of the receiver FIFO. When SET\_RTS is commanded the UARTs automatic RTS mode is selected which then controls the state of the RTS line based on its FIFO. If the FIFO becomes critically full it will automatically negate the signal but will otherwise assert it. This means that the UART will automatically protect its own FIFO from overruns as long as HW flow control is supported by the remote transmitter.

The  $\mu$ Tasker serial driver will also automatically control the RTS line when the input buffer becomes critically full.

To perform HW flow control in the opposite direction, the CTS line can be configured to automatically control the transmitter. This mode is automatically configured when the HW flow control mode is configured [tInterfaceParameters.Config |= RTS\_CTS].

The bit TXCTSE set in UARTX\_MODEM is set so that the UART automatically suspends transmission when the input is negated. No CTS interrupt is generated so the control is purely performed in hardware. The state of the CTS line cannot be specifically requested.

**UART DMA transmission** is supported when the define <code>SERIAL\_SUPPORT\_DMA</code> is enabled in the project. In this case each individual UART can be configured for either DMA or interrupt operation when the UART is configured:

DMA channels triggered by peripherals use the DMA MUX. When peripheral DMA is in operation the DMA MUX is automatically enabled and configured to suit the peripheral. The DMA channel used by each peripheral is configurable in  $app_hw_kinetis.h$  in the DMA settings block, whereby the channels must be unique for all used ones.

| #define | DMA_UART0_TX_CHANNEL | 3 | // | this DMA channel when using UART 0 transmission driven by DMA |

|---------|----------------------|---|----|---------------------------------------------------------------|

| #define | DMA_UART1_TX_CHANNEL | 4 | // | this DMA channel when using UART 1 transmission driven by DMA |

| #define | DMA_UART2_TX_CHANNEL | 5 | // | this DMA channel when using UART 2 transmission driven by DMA |

| #define | DMA_UART3_TX_CHANNEL | 6 | // | this DMA channel when using UART 3 transmission driven by DMA |

| #define | DMA_UART4_TX_CHANNEL | 7 | // | this DMA channel when using UART 4 transmission driven by DMA |

| #define | DMA_UART5_TX_CHANNEL | 8 | // | this DMA channel when using UART 5 transmission driven by DMA |

The priority of the channel used is set to the the same level as the channel's number (eg. if DMA channel 4 is used for a particular UART transmitter its DMA priority is also 4).

If it is necessary to change priorities of the channels this should be performed by using a set of channel priority definitions which will be set at initialisation:

```

#define DMA_CHANNEL_0_PRIORITY 15

#define DMA_CHANNEL_1_PRIORITY 14

#define DMA_CHANNEL_2_PRIORITY 13

..

#define DMA_CHANNEL_14_PRIORITY 1

#define DMA_CHANNEL 15 PRIORITY 0

```

Changing priorities after initialisation is not supported due to the risks involved but swapping channels used (and so priority settings) is possible at run-time. It is to be noted that any DMA operation that occurs when priority levels are being changed and there is a conflict (two channels with same priority level) this will lead to an error and suspend the DMA attempt. Since it is generally not realistic to change priorities safely without disabling all DMA operation temporarily (and possibly losing some peripheral data) this is avoided.

Reception via DMA is less common due to the fact that there is no indication of individual characters being receive d(without polling) but can be enabled using

Each complete buffer received results in a message with its character content to be informed of. Half-buffers are used if the flag UART\_RX\_DMA\_HALF\_BUFFER is set as well when the interface is opened/configured.

#### Again each UART channel used needs to be defined to a particular DMA channel

| #define DMA_UART0_RX_CHANNEL | 9  | DMA channel<br>ption driven | 2 | UART | 0 |

|------------------------------|----|-----------------------------|---|------|---|

| #define DMA_UART1_RX_CHANNEL | 10 | DMA channel ption driven    | 2 | UART | 1 |

| #define DMA_UART2_RX_CHANNEL | 11 | DMA channel                 | 2 | UART | 2 |

| #define DMA_UART3_RX_CHANNEL | 12 | DMA channel ption driven    | 2 | UART | 3 |

| #define DMA_UART4_RX_CHANNEL | 13 | DMA channel ption driven    | 2 | UART | 4 |

| #define DMA_UART5_RX_CHANNEL | 14 | DMA channel ption driven    | - | UART | 5 |

#### **Ethernet Controller**

Warning: due to a conflict in the sharing of the MII0\_RXER and JTAG\_TRST lines MII0\_RXER (optional line) cannot be used together with a JTAG debugger. This is not a problem when debugging using the SWD interface, such as the inbuilt debugger on the tower kit. When using JTAG the MII0\_RXER function should not be used and can be disabled by setting the define JTAG\_DEBUG\_IN\_USE\_ERRATA\_2541.

The Ethernet controller is basically compatible with the one in the Coldfire. It has the same control register set and MIB counters.

In addition it has IEEE1588 support and a capture/compare block.

The tower kit supports RMII mode of operation at the TWR-SER board and the K60 board is defined for operation in this configuration. This means that the following signals are required for Ethernet operation (see also the discussion about the clock setting in the main text in the section about recommended jumper configurations):

- MII\_MDIO (PB0 ALT 4) maintenance connection to PHY serial data line

- MII\_MDC (PB1 ALT 4) maintenance connection to PHY serial clock

- RMII\_CRS\_DV (PA14 ALT 4)

- RMII\_RXD[0] (PA13 ALT 4)

- RMII\_RXD[1] (PA12 ALT 4)

- RMII\_RXER (PA5 ALT 4)

- RMII\_TXD[0] (PA16 ALT 4)

- RMII\_TXD[1] (PA17 ALT 4)

- RMII\_TXEN (PA15 ALT 4)

- RMII\_REF\_CLK this is taken from the internal clock OSCERCLK, which is a buffered signal from the EXTAL input (oscillator or crystal). This signal must be 50MHz for the RMII Ethernet mode to operate. The signal is also available as dedicated input on some device, such as the FPU parts, which means that the main oscillator is not required to be 50MHz.

The define ETHERNET\_RMII should be used.

The following differences exist in comparison to the M52259 Kirin3 (as reference)

- It is not possible to write to the MIB block. When writes are attempted a hard fault occurs (to clear the MIB a memcpy() call is made with the Kirin3). The MIBC register contains a new bit called MIB\_CLEAR which can be used to command a clear instead.

- 2) K60 can operate in RMII mode at 100MHz.

- 3) The CRC32 can be automatically stripped when receiving Ethernet frames.

- 4) The Ethernet buffer descriptors operate in big-endian mode. This means that their content flag format is byte-swapped in comparison to when operating on a Coldfire. In addition the content length (saved as short word in the descriptors) needs to be converted as do any memory pointers in the descriptors.

- 5) The Ethernet buffer descriptors operate in legacy mode by default, meaning that Coldfire code (with the exception of little-endian conversions) operates without any large modifications. The buffer descriptors can also work in extended mode this mode has not yet been implemented.

- 6) The Kinetis EMAC automatically pads transmitted frames to 64 byte length

An interesting feature in the EMAC is the new support for IP checksum offloading. This allows the HW to automatically check or generate checksums for IP, ICMP, TCP and UDP frames (IPv4 and IPv6), which make the operation much more efficient than when SW needs to do this – see the following for some figures showing the loading of check sum calculation: http://www.utasker.com/docs/uTasker/uTaskerBenchmarks.PDF

To enable check sum offloading in transmission IP headers enable IP\_TX\_CHECKSUM\_OFFLOAD

To enable check sum offloading in transmission IP protocol payloads enable IP\_TX\_PAYLOAD\_CHECKSUM\_OFFLOAD

Enable both to use both transmission offloading features.

To automatically discard frames received with IP header or protocol checksums the defined IP\_RX\_CHECKSUM\_OFFLOAD is enabled. Since no frames will be received with such errors the IP software also doesn't need to verify them.

#### PHY and RMII

It is to be noted that RMII mode of operation requires more effort to match the Ethernet controller's mode to the present line characteristics. Since the PHY is the part actually monitoring the line and informing of line changes (link up, link down, link characteristic changes) it is important that the PHY and Ethernet work together. Essentially all link state changes are reported via its interrupt line and the Ethernet driver can change the Ethernet controllers mode settings accordingly. This is performed in the Ethernet driver to ensure that the RMII mode of the Ethernet controller (10M or 100M, half-duplex or full-duplex) is each time synchronised to that which is being detected by the PHY. The Freescale tower kit operates in RMII mode although the Kinetis itself can be connected in MII mode, whereby the adaptation is then controlled automatically by the interface itself.

Communication between the PHY and the Kinetis takes place via the MII management channel. The serial speed is usually 2.5MHz but it is run at 800kHz in the tower kit since the lines are long (they traverse the backplane) and the weak pull-up on the data line, together with the backplane capacitance otherwise result in a speed limitiation.

When there is no communication between the PHY and the Kinetis the MII management channel's clock is stopped wherever possible to reduce interference and save (a small amount of) power.

#### FLASH

The X parts contain FlexNVM and FlexRAM. The N parts contain just program FLASH which can however also be programmed by the application. Since the most common parts are the N parts these will be concentrated on here.

The FLASH controller allows simple programming and erasing of FLASH. Flash programming can be performed on long words (cumulative programming of single long words is expressly forbidden and so is to be avoided) and larger buffer sizes too.

FLASH can be erased in sectors (2k in size for non-FPU types and 4k for FPU types) or in blocks (256k in 512k parts). The FLASH granularity is thus 2k resp. 4k (smallest erasable block).

Programming of a long word takes typically 50us. Erasing a sector takes typically 20ms (maximum 100ms). A block erase takes typically 160ms (maximum 800ms).

Long word programming is however only possible on non-FPU parts because the FPU parts use "phrase" programming instead (based on 8 bytes)

The program FLASH is divided into two banks (blocks) and it is possible to erase/program in one bank when code is being executed from the other. It is not possible to execute code from a bank in which a write or erase operation is being performed and so generally the programming routine runs from RAM and interrupts need to be avoided if their handlers can cause code in the programming area to be called.

The mass erase command fnMassEraseFlash() is supported by using the "ERASE ALL BLOCKS COMMAND". This deletes all types of internal memory and also removes any block protection security and so can be used to unlock general security settings.

#### **Reset and Watchdog**

The mode controller can be read to determine the reason of the last reset. Reasons range from power on reset, external reset, wakeup reset, watchdog reset to loss-of-clock reset.

The routine extern unsigned char fnAddResetCause(CHAR \*ptrBuffer) can be used to fill a string buffer with the reset cause and is displayed on the administrator web page when the web server demo is active.

The internal watchdog operates out of reset and is clocked by default from the external system clock and it must be either reconfigured or stopped within a short period of time of 256 bus clock cycles after reset. It is therefore necessary to perform this activity before the initialisation code performs variable initialisation to avoid a watchdog reset taking place.

The watchdog is set to a value of 2s by default in the  $\mu$ Tasker demo project and can be disabled by holding SW1 on the TWR-K60N512 board. It is triggered every 200ms by the watchdog task when the system is operating normally. When triggering the watchdog interrupts are temporarily disabled so that the trigger sequence, that much be completed within 20 bus cycles, is not disturbed. The trigger sequence involves writing the sequence 0xa602 and 0xb480 to the refresh register.

The Kinetis includes a further watchdog module called the external watchdog monitor which is designed to reset external circuitry in case of a software error. It doesn't reset internal circuitry since this is the job of the internal watchdog.

The user can command a reset of the board by using the routine <code>extern void fnResetBoard(void)</code>. This uses the Cortex's reset request to initiate the reset the fact is signalled in the mode controller's reset cause register after the next reset.

<u>Important notes about debugging</u>: Due to the fact that the watchdog configuration needs to be performed quickly after a reset it is recommended to allow the debugger to run to main() when it connects. This allows it to immediately start the processor and allow the code to quickly configure the watchdog as required – even with active watchdog configured it can be set up to stop when the debugger pauses execution (this is the default configuration in the project).

If the start-up code needs to be stepped through, the watchdog unlocking sequence should be avoided since it will result in a reset due to the fact that the stepping has taken too long to reach the unlocking location. See also the following forum post for details of speeding up the code to reach the watchdog unlocking sequence: http://www.utasker.com/forum/index.php?topic=1664.0

#### Interrupts

The size of the interrupt vector table depends on the number of interrupts that are possible – the K60 requires 432 bytes to hold its maximum total 216 interrupt vectors. If interrupt vectors located higher in the vector table are not actually used less space would in fact be needed, but the 432 bytes space is reserved to accommodate all possibilities.

Rather than use the interrupt vectors directly from fixed locations at the start of FLASH they are entered into SRAM only when needed. The first 432 bytes of SRAM are reserved for this use, meaning that linker script files allow the first used address to be 0x1ff01b0. The Cortex M4 vector table offset register is set to 0x1ff0000 so that interrupt vectors are taken from there.

This strategy allows interrupt handlers to be exchanged in SRAM during operation and also is suited to systems operating with a boot loader since its interrupt vectors cannot be fixed at the start of FLASH, which is occupied by the boot start-up code.

It is to be noted that not all Kinetis parts have compatible interrupt vector tables. For example, low power parts that are specified for 50MHz have less interrupts and a correspondingly smaller table with interrupt vector IDs at different location to its 75MHz or 100MHz parts.

#### **Port Interrupts**

Each GPIO can be used as an interrupt line (the Kinetis doesn't have IRQ0, IRQ1, IRQ2... as the Coldfire has).

The port interrupt support is enabled by the define SUPPORT\_PORT\_INTERRUPTS (in app\_hw\_kinetis.h). This allows individual interrupt handler routines to be defined to each of the port pins, whereby the Kinetis has one interrupt vector for each of the ports available (port A to port E). If any ports are not required for interrupt generation they can be specifically excluded from the code by setting NO\_PORT\_INTERRUPTS\_PORTA, NO\_PORT\_INTERRUPTS\_PORTB, etc. as appropriate.

The following shows how a port interrupt can be simply defined:

This shows a level sensitive interrupt being configured on port A, bit 27. Also a pull-up resistor is being configured in the port input.

The interrupts are flexible and can be falling edge, rising edge or both-edge sensitive. They can also be level high or level low sensitive. The type can be selected by defining IRQ\_FALLING\_EDGE, IRQ\_RISING\_EDGE, IRQ\_BOTH\_EDGES, IRQ\_LOW\_LEVEL **or** IRQ\_HIGH\_LEVEL **as** interrupt\_setup.int\_port\_sense **value**.

An interrupt can be set to multiple port pins by defining more than one input belonging to the port as interrupt\_setup.int\_port\_bits value. For example, interrupt\_setup.int\_port\_bits = (PORTA\_BIT27 | PORTA\_BIT18 | PORTA\_BIT10); will cause the same handler to be called for matching states or changes on any of these pins.

Since the port interrupt interface handles clearing of the interrupt source the user handler doesn't need to be concerned with these details.

#### Periodic Interrupt Timers (PIT)

The K70 has 4 PITs. These are however not the same as the ones in the Coldfire.

Improved features include 32 bit counters that can also trigger DMA transfers or ADC conversions. Each of the PITs is realised as a down counter which are clocked from the peripheral bus clock.

The following example shows how a PIT (Pit 1 shown) can be simply configured for a single shot interrupt:

```

PIT_SETUP pit_setup; // interrupt configuration parameters

pit_setup.int_type = PIT_INTERRUPT;

pit_setup.int_priority = PITI_INTERRUPT_PRIORITY;

pit_setup.count_delay = PITI_SINGLE_Y(3245); // 3245us delay

pit_setup.mode = PIT_SINGLE_SHOT; // one-shot interrupt

pit_setup.ucPIT = 1; // use PITI

fnConfigureInterrupt((void *)&pit_setup); // enter interrupt for PIT1 test

```

When the timer has fired it will be automatically stopped. If there are no other PITs active the PIT module will also be automatically powered down.

To start a periodic interrupt the mode PIT\_PERIODIC is used instead. In this case it will run until stopped with the mode command PIT\_STOP. Again, if there are no other PITs operating when the PIT is stopped the module will be automatically powered down.

Since the PITs have 32 bit counters and are clocked at the bus rate, with maximum speed of 50MHz, the maximum period that they can be set to at the highest bus speed is about 85s.

### FlexBus

The FlexBus has 6 independent chip selects and is thus almost identical to the FlexBus in the M520X Coldfires (also the Kirin3 M5225X, which however has only two independent chip select lines).

It has one additional register called the Chip Select Port Multiplexing Control Register which controls the multiplexing of some of the available signals, depending on the bus interface type required.

The FlexBus is intended mainly for multiplexed bus operation whereby the data and address bus widths are part dependent. The FlexBus memory range is between 0x60000000 and 0cdfffffff.

The K60 supports FB\_AD0..FB\_AD31 (a full 32 bit multiplexed bus) and FB\_A16..FB\_A29 as non-multiplexed address bus. The bus lines used are selected by the port peripheral functions alone.

The TWR-K60N512 can control the TFT display on the TWR-LCD extension module via a 16 bit multiplexed bus, whereby the lines FB\_AD0..FB\_AD15 are used as data bus (note that the 16 bit accesses can be controlled to occur on either FB\_AD0..FB\_AD15 or FB\_AD16..FB\_AD31; in comparison the Mini-FlexBus in the Kirin3 has only FB\_AD..FB\_AD15.

The line FB\_AD16 is used as an address line to select between command and data access and the control lines FB\_CS0 and FB\_RW are the only other signals required for complete control.

#### **DMA Controller**

The K60 has a 16 channel extended DMA controller.

When the define DMA\_MEMCPY\_SET is enabled the uMemcpy() and uMemset() routines use a single channel of the eDMA controller to perform the memory transfers. This is several times faster than performing the copy via the CPU. The channel is given the lowest priority and is allowed to be temporarily stalled by higher priority DMA channels while operating. Should an IRQ perform a copy based on these functions any active copy is protected and the IRQ will then use a conventional copy instead.

The DMA channel used for the memory copy routines is defined by

#define DMA\_MEMCPY\_CHANNEL 15

The priority of the used channel is set to 0 (lowest) and the priority of the used channel (when not 0) is set to channel 0 so that no two channels have the same priority, which is otherwise illegal.

It is to be noted that only the first 4 DMA channels support periodic transfers and so must be used together with PITs if used in this mode.

All devices have DMA channels 0..15. The devices with FPU have a second DMA group with channels 16..31. Since the groups' DMA channels are prioritised between 0 and 15 (15 is highest priority) and no two channels may have the same priority also the groups have their own priorities that much ne unique. The group 0 (DMA channels 0..15) are set to group priority 0 and the group 1 (DMA channels 16..31) are set to group priority 1 in the  $\mu$ Tasker project to ensure that they don't collide. This means that the user can assign DMA channels from group 1 (when using devices with this) if they should have higher priorities than those in group 0.

#### RTC

The K60 has a low power Real Time Clock module with an independent power supply (VBAT), a 32.768kHz oscillator and optional 1Hz square wave output. The 32.768kHz clock output can also be supplied to the rest of the chip if required. The crystal can be calibrated between 0.12 ppm and 3906 ppm.

The RTC is not a RTC which counts second, minutes, hours, days, etc. but is a 32 bit seconds counter. This means that conversion to actual time/dates needs to be handled in software, as are such details about the number of days in a months and when a leap-year has to be considered.

Furthermore the power to the RTC is always taken from the VBAT input, also when the processor is powered up. This means that there is battery drain even when the processor is powered if this is not solved by external hardware and the RTC cannot be used without VBAT, even if it doesn't need to operate when normal power has been removed (of course this is not a problem since VBAT can also be simply connected to the general power supply in such a usage case).

The VBAT voltage level should be between 1.71V and 3.6V. The typical current consumption with active 32.768 kHz oscillator operating is 550nA, which is a good value for an internal RTC. However there are no additional user-registers that can be retail values in the module, which are often available in RTC modules.

Software should not try to access the RTC operating registers when the VBAT is not connected since this will result in a bus error.

There are 4 pins that can be assigned to the RTC.

EXTAL32, XTAL32 - for 32.768kHz crystal connection

RTC\_CLKOUT - for 1Hz square wave output

RTC\_WAKEUP – open-drain, active low output to wake up external devices when the RTC interrupt occurs. This asserts when the device is powered down and can thus be used to start a system out of this mode at a pre-defined point in time *This output is not available on all device types*.

The RTC interrupt can be used to wake the chip from any low power mode.

The K40 doesn't seem to implement the seconds interrupt in the RTC. A seconds interrupt can however be achieved by using an alarm interrupt always set to the next second.

# Note that the RTC crystal should be positioned close to the device and its signals should be short and protected against cross-talk from other signal lines. The start-up time is typically 1s and this time should be waited after initial activation before using the RTC or its clock at other modules.

The μTasker project implements a RTC API including Gregorian date/time from the 1s interrupt. It emulates the RTC in some Coldfire to additionally allow minutes, hours, days, stop-watch interrupts as well as date/time alarm interrupt. More information is available at <a href="http://www.utasker.com/forum/index.php?topic=1656.0">http://www.utasker.com/forum/index.php?topic=1656.0</a>

### ADC

The Analogue to Digital Converter (ADC) module used in the Kinetis devices supports up to 4 differential analogue inputs and up to 24 single-ended analogue inputs. Based on linear successive approximation it offers up to 16-bit resolution (note that several resolution modes are possible and the low power ADC achieves up to 14 bit of actual accuracy).

The ADC supports a self-calibration mode.

Using its compare registers it can compare ADC results and also ranges.

The following table shows the pins that are used by the ADCs in the K60 and also multiplexed with ports:

| ADC name  | Port  | Function |

|-----------|-------|----------|

| ADC0_SE10 | PTA7  | ALT 0    |

| ADC0_SE11 | PTA8  | ALT 0    |

| ADC1_SE17 | PTA17 | ALT 0    |

| ADC0_SE8  | PTB0  | ALT 0    |

| ADC0_SE9  | PTB1  | ALT 0    |

| ADC0_SE12 | PTB2  | ALT 0    |

| ADC0_SE13 | PTB3  | ALT 0    |

| ADC1_SE10 | PTB4  | ALT 0    |

| ADC1_SE11 | PTB5  | ALT 0    |

| ADC1_SE12 | PTB6  | ALT 0    |

| ADC1_SE13 | PTB7  | ALT 0    |

| ADC1_SE14 | PTB10 | ALT 0    |

| ADC1_SE15 | PTB11 | ALT 0    |

| ADC0_SE14 | PTC0  | ALT 0    |

| ADC0_SE15 | PTC1  | ALT 0    |

| ADC0_SE4  | PTC2  | ALT 0    |

| ADC1_SE4b | PTC8  | ALT 0    |

| ADC1_SE5b | PTC9  | ALT 0    |

| ADC1_SE6b | PTC10 | ALT 0    |

| ADC1_SE7b | PTC11 | ALT 0    |

| ADC0_SE5  | PTD1  | ALT 0    |

| ADC0_SE6  | PTD5  | ALT 0    |

| ADC0_SE7  | PTD6  | ALT 0    |

| ADC1_SE4a | PTE0  | ALT 0    |

| ADC1_SE5a | PTE1  | ALT 0    |

| ADC1_SE6a | PTE2  | ALT 0    |

| ADC1_SE7a | PTE3  | ALT 0    |

| ADC0_SE17 | PTE24 | ALT 0    |

| ADC0_SE18 | PTE25 | ALT 0    |

Some ADC inputs have dedicated pins:

ADC0\_DP0 / ADC0\_DM0 ADC0\_DP1 / ADC0\_DM1 PGA0\_DP / PGA0\_DM ADC0\_DP3 / ADC0\_DM3 ADC1\_DP0 / ADC1\_DM0 ADC1\_DP1 / ADC1\_DM1 PGA1\_DP / PGA1\_DM ADC1\_DP3 / ADC1\_DM3

These are the inputs with differential capabilities and the programmable gain amplifiers.

It is to be noted that the analogue functions are the default functions for the ADC pins.

Conversion time was tested with several setups as reference (K60 running at 100MHz with bus clock at 50MHz):

ADC clock Bus-clock/2 - Pre-scaler /8 - 16 bit mode single-ended - long-sample (24 clocks) – 32x hardware averaging = 460us

Pre-scaler reduced to /1 = 56us

+ Short-Sample mode = 32.4us

- + Bus not divided by 2 = 16us

- + No hardware averaging = 700ns

In 16 bit mode the ADC clock should however be restricted to the range of 2MHz to 12MHz, meaning that not all conversion times can be achieved to specification. Practically, the bus clock needs to be divided by 8 to clock with 6.25MHz, which gives a minimum conversion time of 5.6us – or theoretical maximum sample rate of 178kHz. If the ADC clock can be controlled to be exactly 12MHz the minimum conversion time of 2.6us and maximum sample rate of 383kHz is obtained in 16 bit mode (remembering that this will achieve about 13 bits of accuracy).

The slowest rate using continuous conversion above is equivalent to 2.17kHz.

ADC conversion can be triggered by software, whereby this can be a single conversion or continuous conversion mode.

Hardware triggering is also possible although the source is chip-dependent. The K60 allows the following trigger sources:

- External trigger pin PDBn\_EXTRG

- High speed comparators (0, 1 or 2)

- PIT 0, 1, 2 or 3

- FTP0, 1 or 2

- RTC alarm or RTC seconds

- Low power timer

The triggering source is configured in SIM\_SOPT7.

ADC conversions can be used to trigger DMA transfers.

The K60 has 2 ADC controllers. These both support up to 24 single ended inputs and 4 differential inputs. However only one of the inputs is possible at a time. The two ADC controllers thus allow two inputs to be samples at the same time. If a higher number of inputs are to be sample the sampling must be multiplexed between these inputs under software control.

#### DAC

The 12 bit Digital to Analogue Converter (DAC) supports DMA operation. The K60 has two DACs and their outputs can drive external pins or be connected internally as reference to the analogue comparator, ADCs or Op-Amp.

The DAC can also be used together with DMA and includes a FIFO especially for this mode of operation.

The 1.2V VREF\_OUT or the VDDA voltage can be used as DAC reference. Some degradation of ADC performance is to be expected if VREF\_OUT is used by both ADC and DAC at the same time; this is due to the DAC switching. VREF\_OUT always need an external load capacitor connected to it spin.

Each DAC has an external trigger input called ADCxSC1A\_COCO. This can be also be triggered on ADC conversion completion.

It is to be noted that the comparator modules also contain 6-bit internal DACs. This are internal signals only and are not available on any external pins.

# I<sup>2</sup>C

The K60 has 2 I<sup>2</sup>C controllers. They are more advanced that the I<sup>2</sup>C controllers in the M522XX since they support System Management Bus Specification, version 2, have an additional programmable glitch input filter, range I<sup>2</sup>C address support and can also detected an SCL line which is stuck at '0' for too long.

The I<sup>2</sup>C controllers can usually be mapped to various pins on the device. The following table shows the possibilities.

| I2C0       | I2C0_SDA         | I2C0_SCL         |

|------------|------------------|------------------|

| I2C0_B_LOW | Port B1 (Alt 2)  | Port B0 (Alt 2)  |

| default    | Port B3 (Alt 2)  | Port B2 (Alt 2)  |

| I2C0_ON_D  | Port D9 (Alt 2)  | Port D8 (Alt 2)  |

| I2C1       | I2C1_SDA         | I2C1_SCL         |

| I2C1_ON_E  | Port E0 (Alt 6)  | Port E1 (Alt 6)  |

| default    | Port C11 (Alt 2) | Port C10 (Alt 2) |

#### SPI

The K60 has 3 SPI interfaces. These are different from the QSPI interface in the Coldfire devices and can also work in slave mode. They are called DSPI because they can also be driven by DMA and have optional 4 deep receive and transmit FIFOs.